SDIO(Secure Digital lnput and Output),即安全数字输入输出接口。SDIO 总线协议是由 SD 协议演化而来,它主要是对 SD 协议进行了一些扩展。

SDIO 总线主要是为 SDIO 卡提供一个高速的 I/O 能力,并伴随着较低的功耗。SDIO 总线不但支持 SDIO 卡,而且还兼容 SD 内存卡。支持 SDIO 的设备比如手机和相机不仅能支持 SD 卡,TF 卡,随着 SDIO 硬件设备的扩充 SDIO 总线的外围能够支持更多的 SDIO 设备比如Bluetooth,WIFI,GPS,Camera sensor 等,它们的识别过程跟 SD 卡类似,主要差别是在 SD 协议的基础上做了些扩展。

图 1 SDIO 总线通信原理国产 ARM + FPGA 架构介绍与优势

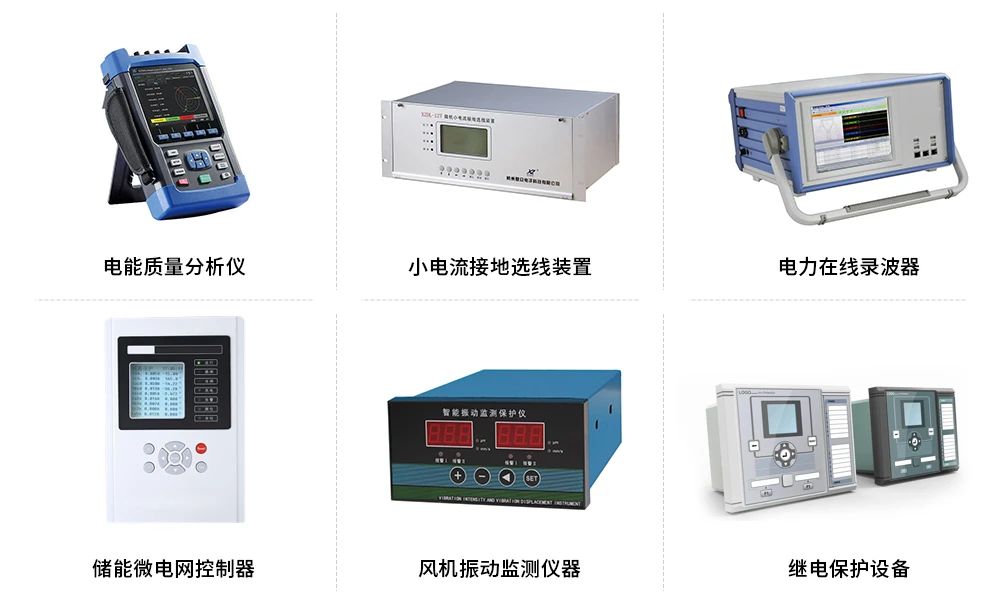

近年来,随着中国新基建、中国制造 2025 规划的持续推进,单 ARM 处理器越来越难胜任工业现场的功能要求,特别是如今能源电力、工业控制、智慧医疗等行业,往往更需要 ARM + FPGA 架构的处理器平台来实现例如多路 / 高速 AD 采集、多路网口、多路串口、多路 / 高速并行 DI/DO、高速数据并行处理等特定功能,因此 ARM + FPGA 架构处理器平台愈发受市场欢迎。

因此,创龙科技一年前正式推出了基于全志 T3 + 紫光同创 Logos 处理器设计的 ARM + FPGA 全国产工业核心板,国产化率达 100%。

全志 T3 为准车规级芯片,四核 ARM Cortex-A7 架构,主频高达 1.2GHz,支持双路网口、八路 UART、SATA 大容量存储接口,同时支持 4 路显示、GPU 以及 1080P H.264 视频硬件编解码。另外,创龙科技已在 T3 平台适配国产嵌入式系统翼辉 SylixOS,真正实现软硬件国产化。

紫光同创 Logos PGL25G/PGL50G FPGA 在工业领域应用广泛,逻辑资源分别为 27072/51360,与国外友商产品 pin to pin 兼容,主要用于多通道 / 高速 AD 采集或接口拓展。因其价格低、质量稳定、开发环境易用等优点,受到工业用户的广泛好评。尤其是开发环境,最快 3 天可完成从国外友商产品到紫光同创产品的切换。

图 2 ARM + FPGA 典型应用场景

国产 ARM + FPGA 的 SDIO 通信案例介绍

本章节主要介绍全志科技 T3 与紫光同创 Logos 基于 SDIO 的 ARM + FPGA 通信方案,使用的硬件平台为:创龙科技 TLT3F-EVM 工业评估板。最终实测写速率为 5.678MB/s,读速率为 5.744MB/s,误码率为 0。

案例功能

该案例实现 T3(ARM Cortex-A7) 与 FPGA 的 SDIO 通信功能。

RM 端 sdio_test 案例实现 SDIO Master 功能,具体如下:

(1)打开 SDIO 设备节点,如:/dev/generic_sdio0;

(2)发送数据至 SDIO 总线,以及从 SDIO 总线读取数据;

(3)校验数据,然后打印读写速率、误码率。

FPGA 端 dram_sdio 案例实现 SDIO Slave 功能,具体如下:

(1)FPGA 将 SDIO Master 发送的数据保存至 DRAM;

(2)SDIO Master 发起读数据时,FPGA 从 DRAM 读取数据,并通过 SDIO 总线传输至 SDIO Master。

图 3 ARM 端程序流程图

案例演示

评估板上电后,请先固化 FPGA 案例 dram_sdio_xxx.sfc 可执行程序至 FPGA 端,FPGA 需在 ARM 驱动加载前完成初始化。再将 ARM 端可执行文件 sdio_test、"driver\bin\generic_sdio.ko" 驱动拷贝至评估板文件系统任意目录下。

评估板上电启动,在 generic_sdio.ko 驱动所在路径下,执行如下命令加载驱动。

Target#insmod -f generic_sdio.ko

图 4

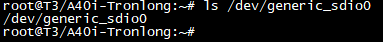

执行如下命令,可查看设备节点。

Target#ls /dev/generic_sdio0

图 5

执行如下命令,可查询程序命令参数。

Target#./sdio_test -h

图 6

执行如下命令,ARM 通过 SDIO 总线写入随机数据至 FPGA DRAM,然后读出数据、进行数据校验,同时打印 SDIO 总线读写速率和误码率,如下图所示。

Target#./sdio_test -d /dev/generic_sdio0 -s 1024

参数解析:

-d:设备节点路径;

-s:设置传输数据大小,单位为 Byte。

图 7

本次测试 SDIO 总线通信时钟频率为最高 50MHz,则理论通信速率为:(50 x 4 / 8)MB/s = 25MB/s。从上图可知,则可以清晰看到实测速率结果。

备注:实测速率相比理论速率偏低,与 ARM 端驱动和 FPGA 端逻辑实现、IP 核配置有关。